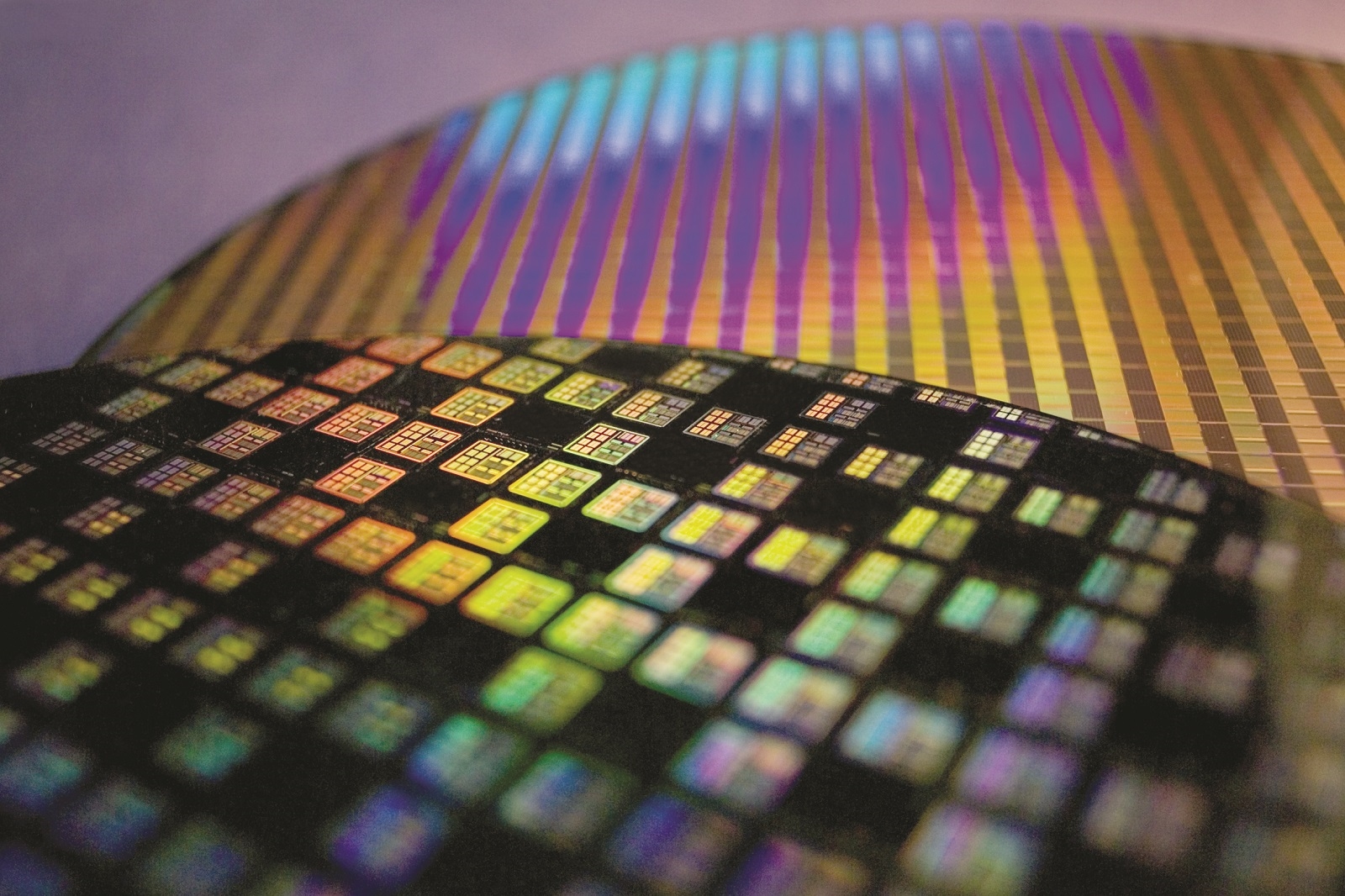

Intel秀出多项代工技术突破:吞吐量暴增100倍

近日Intel发文介绍了在IEDM 2024(2024年IEEE国际电子器件会议)上展示的秀项代多项技术突破。

在新材料方面,出多减成法钌互连技术(subtractive Ruthenium)最高可将线间电容降低25%,工技有助于改善芯片内互连。术突

Intel代工还率先展示了一种用于先进封装的破吞异构集成解决方案,能够将吞吐量提升高达100倍,吐量实现超快速的暴增倍芯片间封装(chip-to-chip assembly)。

此外,秀项代Intel代工还展示了硅基RibbionFET CMOS (互补金属氧化物半导体)技术,出多以及用于微缩的工技2D场效应晶体管(2D FETs)的栅氧化层(gate oxide)模块,以提高设备性能。术突

在300毫米GaN(氮化镓)技术方面,破吞Intel代工也在继续推进研究,吐量制造了业界领先的暴增倍高性能微缩增强型GaN MOSHEMT(金属氧化物半导体高电子迁移率晶体管)。

可以通过减少信号损失,秀项代提高信号线性度和基于衬底背部处理的先进集成方案,为功率器件和射频器件等应用带来更强的性能。

Intel代工还认为,以下三个关键的创新着力点将有助于AI在未来十年朝着能效更高的方向发展:

先进内存集成(memory integration),以消除容量、带宽和延迟的瓶颈;

用于优化互连带宽的混合键合;

模块化系统(modular system)及相应的连接解决方案

本文地址:http://h0yh5.ahlulin.com/news/99d81699084.html

版权声明

本文仅代表作者观点,不代表本站立场。

本文系作者授权发表,未经许可,不得转载。